- 全部

- 默认排序

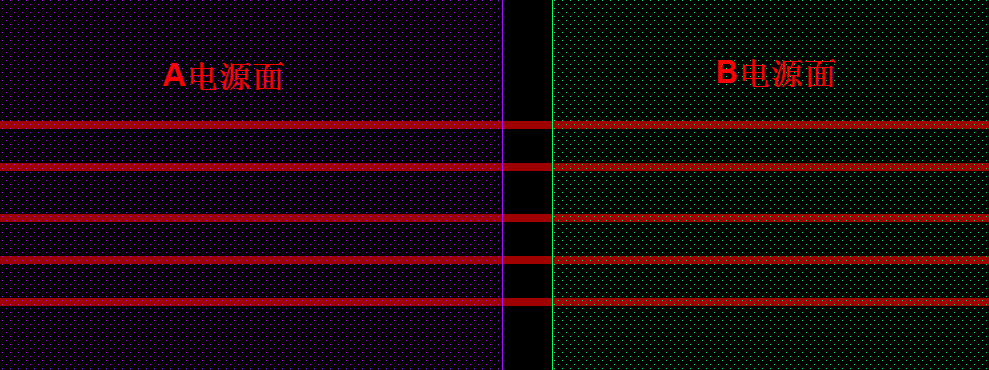

答:我们PCB中的信号都是阻抗线,是有参考的平面层。但是由于PCB设计过程中,电源平面的分割或者是地平面的分割,会导致平面的不完整,这样,信号走线的时候,它的参考平面就会出现从一个电源面跨接到另一个电源面,这种现象我们就叫做信号跨分割。跨分割的现象如图1-52所示。

答:ICT,In Circuit Tester,自动在线测试仪,是印制电路板生产中重要的测试设备,用于焊接后快速测试元器件的焊接质量,迅速定位到焊接不良的引脚,以便及时进行补焊。

答:端接,Butt Joint,是指消除信号反射的一种方式。在高速PCB设计中,信号的反射将给PCB的设计质量带来很大的负面影响,采用端接电阻来达到线路的阻抗匹配,是减轻反射信号影响的一种有效可行的方式。端接,分为一下两类:

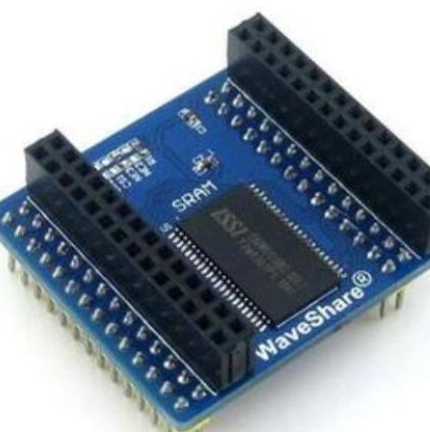

答:PCB设计中常用的存储器有如下几种:Ø SDRAM,Synchronous Dynamic Random Access Memory(同步动态随机存储器)的简称,SDRAM采用3.3v工作电压,带宽64位,SDRAM将CPU与RAM通过一个相同的时钟锁在一起,使RAM和CPU能够共享一个时钟周期,以相同的速度同步工作,与 EDO内存相比速度能提高50%;

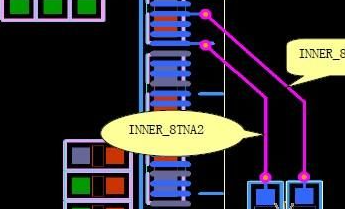

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

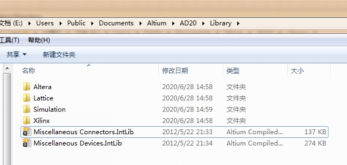

答:AD系统自带的原理图库,在我们进行设计的过程中可以直接调用,可以省去很多绘制的时间封装的时间,但是很多人不清楚他的路径在哪里?下面以AD20版本为例进行说明:路径为C:\Users\Public\Documents\Altium\AD20\Library

基于良好信任,达成长远发展战略,在合伙人的基础上,深圳市凡亿技术开发有限公司与深圳华秋电子有限公司于2021年5月17日达成战略合作伙伴关系,在电子工程师教育、PCB设计、PCB制造等领域展开深度合作,共同推动中国电子产业链的增效降本,为双方创造更大的商业价值。

凡亿双十一第三场活动——F3系列88折限时开启~想学习高速PCB设计的小伙伴们,可以考虑考虑是否要报名学习一下呢?活动期间下单将赠送快捷键鼠标垫任意1款+7把趣味直尺,11号零点还能抢满200-30上不封顶的优惠券哦!心动的小伙伴们,赶紧行动起来吧!

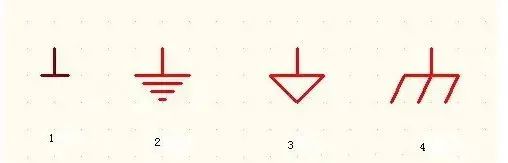

在工程设计中,从参考电平的角度看,都是同一个地,最终都要接到一起获得相同的参考电位。对于地的分开,主要是从布线的角度看的,减少不同电路之间地的干扰,而电源的地不能看成模拟地,信号地也不能看成数字地。

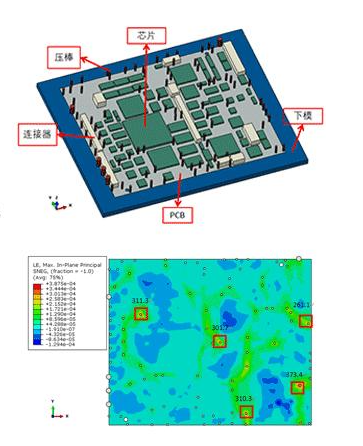

假设现在需要你去绘制一个产品PCB,我们是不是可以从HDMI、AV、RH45、WIFI、DCDC电源、PMU电源管理单元、DDR、FLASH存储器等等模块入手透析这个产品的本质, 了解好每一个模块的基本原理,再掌握每一个模块的PCB布局和PCB布线的要点,然后汇总整个设计, 这时你会发现这个PCB板子基本完成了80%的工作量,剩下的只是模块与模块之间的信号互联了。后续基本通过几个不同难度的全流程案例操作,基本就得心应手了。 训练营第一阶段:理清思路,开启高速无限可能 万丈高楼平地起。开课第一周

扫码关注

扫码关注